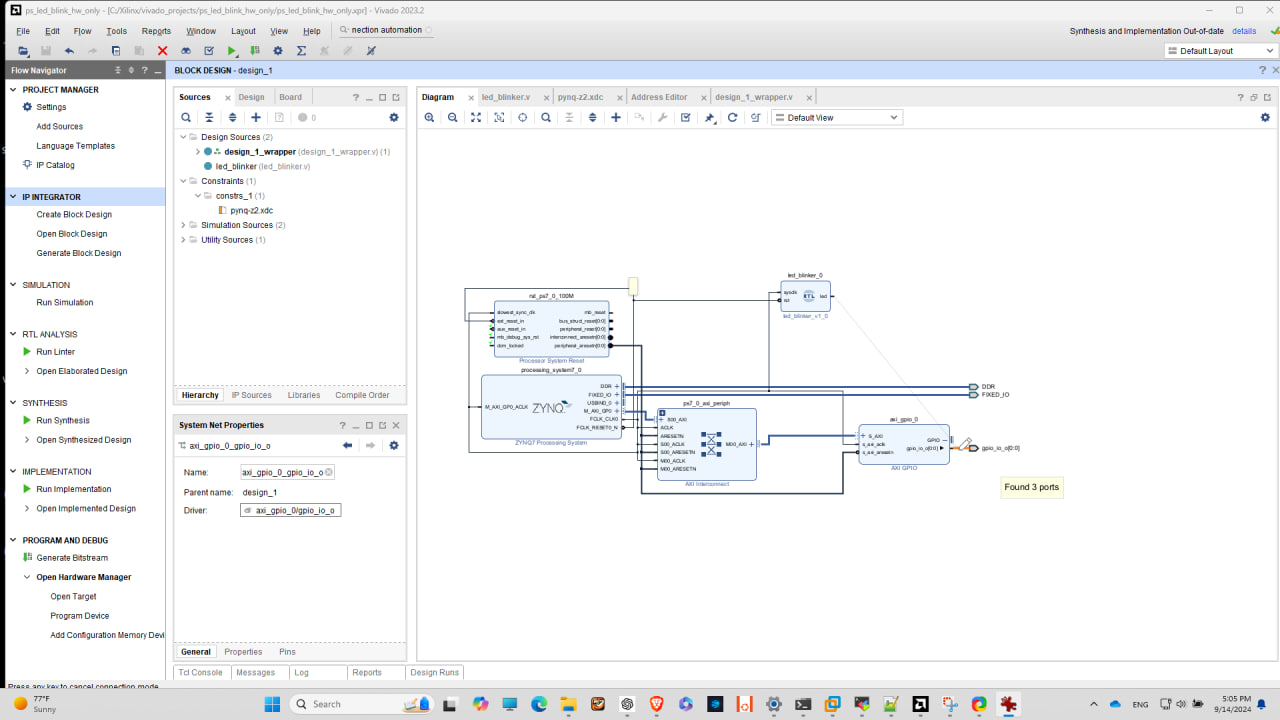

Я использую Vivado 2023.1 и не могу подключить выход RTL модуля к выходу AXI GPIO, который подключен к светодиоду. Пожалуйста, посмотрите на вложение. RTL код ниже

module led_blinker (

input wire sysclk,

input wire rst,

output reg led

);

reg [26:0] counter;

reg led_state;

//Чтобы сигнал сброса работал с PS, убедитесь, что это сигнал на низком уровне

always @(posedge sysclk or negedge rst) begin

if (~rst) begin

counter <= 27'd0;

led_state <= 1'b0;

end else begin

if (counter == 27'd99999999) begin // Скорректируйте для желаемой скорости мигания

counter <= 27'd0;

led_state <= ~led_state;

end else begin

counter <= counter + 1'b1;

end

end

end

always @(*)

begin

led = led_state;

end

endmodule

Ответ

Ваша проблема с подключением выхода RTL-модуля к выходу AXI GPIO, который подключен к светодиоду, может быть вызвана несколькими факторами. Давайте рассмотрим несколько шагов, чтобы помочь вам решить эту проблему.

Шаг 1: Проверьте сигналы ввода/вывода

В вашем RTL-модуле led_blinker выход led объявлен как reg, что является правильным подходом. Однако, чтобы подключить этот выход к блоку AXI GPIO, выход led должен соответствовать ожидаемой ширине входа AXI GPIO. Убедитесь, что указанная ширина совпадает (обычно 8-битная или 1-битная в зависимости от конфигурации).

Шаг 2: Обновите блочный дизайн

-

Добавьте RTL-модуль в вашего проект: Убедитесь, что вы добавили ваш модуль

led_blinkerв блочный дизайн Vivado. -

Создайте интерфейсы: Убедитесь, что для вашего модуля

led_blinkerправильно настроены интерфейсы соединений. Вы можете сделать это, выбрав ваш модуль в блочном дизайне и убедившись, что соответствующие порты подключены корректно. - Подключите выход

ledк AXI GPIO: Проверьте, что вы соединяетеledнапрямую с соответствующим выходом AXI GPIO. Если ваш выходledявляется 1-битным, подключите его к меньшему разряду выходного порта AXI GPIO.

Шаг 3: Проверьте конфигурацию AXI GPIO

-

Настройки AXI GPIO: Убедитесь, что AXI GPIO настроен на режим управления выходами. Для этого откройте свойства AXI GPIO в блочном дизайне и проверьте, правильно ли установлен режим работы (например, ‘All Outputs’ или ‘Single Output’).

- Инициализация AXI GPIO: В вашей тестовой среде или в программном обеспечении встраиваемого процессора убедитесь, что конфигурация AXI GPIO правильно инициализирована и выполнимы ли команды для управления светодиодами.

Шаг 4: Проверьте синтаксис и компиляцию

Убедитесь, что код вашего модуля компилируется без ошибок:

-

Проверьте синтаксис в вашем коде RTL. Вы уже используете правильный синтаксис, но если есть предупреждения или ошибки, их нужно устранить.

- Настройте вашу проектную конфигурацию и убедитесь, что все зависимости и библиотеки упомянуты.

Шаг 5: Симуляция и тестирование

-

Симуляция: Запустите симуляцию вашего проекта и убедитесь, что выход

ledсрабатывает как ожидалось. Это поможет вам понять, есть ли проблемы на уровне RTL или уровня соединения. - Тестирование на аппаратуре: После успешных симуляций загрузите проект на целевую FPGA и проверьте, работает ли все как задумано.

Заключение

Следуя этим шагам, вы сможете разобраться с подключением вашего RTL-модуля led_blinker к AXI GPIO. Если проблемы все еще сохраняются, рекомендуется пересмотреть настройки и, возможно, обратиться к документации Xilinx для дополнительной информации. Убедитесь, что подключения выводов и инициализации корректны, желаемые сигналы приходят к AXI GPIO, и этот блок правильно конфигурирован для работы с вашими выходными данными.